224G SERDES is a high-speed interface technology that underpins next-generation 1.6Tb links. Getting 224G signals from the ASIC to the interconnect and beyond remains a key challenge for the deployment and scaling of 1.6Tb.

Each 1.6Tb link uses 8 lanes of 224G signaling. For Ethernet, this actually runs at 212.5 Gb/s, which includes some overhead for the FEC, called “outer FEC,” based on Reed-Solomon error correcting codes. This provides enough protection for a reliable electrical link from ASIC to module. The IEEE 802.3.dj defines an additional inner FEC (sometimes referred to as FECi) which provides additional coding gain to help close the link for more demanding optical links.

PAM-4 Enables Powerful DSP-based SERDES

It is fair to say we are now entering the third generation of PAM-4 electrical signaling. PAM-4 modulation has been established since 400GbE (using 8 lanes of 53Gbd).

A significant change associated with the move to PAM-4 has been the emergence of powerful Digital Signal Processing (DSP)-based SERDES. Using advanced DSP filters, and DSP-based Clock and Data Recovery (CDR), these SERDES can manage complex channel impairments including loss and reflections that would be extremely challenging with analog-based SERDES. Of course, analog technology still plays a critical role within DSP-based SERDES. Much of the initial processing is done with analog techniques before the Analog to Digital Converter (ADC) inside the DSP block – but DSP techniques underpin the technology to allow 224G, PAM-4 channels.

With such high speeds, channel errors will, and do, occur. This is why the IEEE incorporated FEC in the links. However, as the rates increase and the complexity of the DSP goes up, simple BER measurements are not suitable for the 1.6Tb world.

Why Simple BERT Doesn’t Cut It

Errors occur in transmission. Impairments such as loss, crosstalk, noise and reflects combine in a channel and impact the signal, degrading the signal-to-noise ratio and ultimately leading to errors. Combined with the DSP-based SERDES, it can pass a complex error footprint onto higher level logic such as the Physical Coding Sublayer (PCS) and FEC. More critically, it can result in confusing error bursts that defy analysis with simple BERT tools.

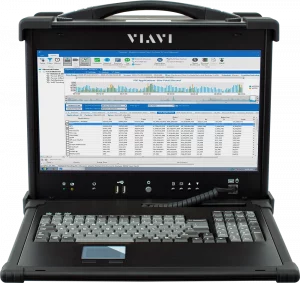

The 224G SERDES that underpin 1.6Tb require far more insightful tools than simple BERT. Building on our experience since 53G PAM-4, VIAVI is now supporting multiple companies in developing, debugging and delivering 1.6Tb devices, based on the latest generation of 224G SERDES.

VIAVI was the first to introduce a 1.6Tb/s testing solution to market and we have been busy supporting the ecosystem by helping customers develop and validate 1.6Tb/s modules around the world

VIAVI Can Help!

Please contact us using these links if you are interested in learning more about our progress testing at 1.6Tb/s: VIAVISolutions.com or VIAVI applications team. And watch for a 1.6Tb workshop we will be hosting in Silicon Valley in 2025. We hope to see you then!

1.6Tb Blog Series

Here are additional blogs in our 1.6Tb testing and validation series. Be on the lookout for more blogs in the future.